## Design & analysis various basic logic gates using Quantum Dot Cellular Automata (QCA)

Mohd. Shayan<sup>1</sup>, Priyanshu Gairola<sup>1</sup>, Nitin Pawar<sup>1</sup>, Keshav Sharma<sup>1</sup>

Anshuman Singh<sup>2</sup>, Dhananjay Singh<sup>2</sup>, Pavan Kumar Shukla<sup>2</sup>, Vinod M. Kapse<sup>2</sup>

<sup>1</sup>Student, Department of Electronics & Communication Engineering, Noida Institute of Engineering and Technology, Greater, Noida

<sup>2</sup>Faculty, Department of Electronics and Communication Engineering, Noida Institute of Engineering and Technology, Greater Noida

**Abstract:** A technology called Quantum Dot Cellular Automata (QCA) offers a far more effective computational platform than CMOS. Through the polarization of electrons, digital information is represented. In comparison to CMOS technology, it is more attractive because to its size, faster speed, feature, high degree of scalability, greater switching frequency, and low power consumption. This paper suggests structures of basic logic gates in the QCA technology. For the aim of verification, the produced circuits are simulated, and their results are then compared to those of their published counterparts. The comparison outcomes provide hope for adding the suggested structures to the collection of QCA gates.

**Keywords** - Logic gates, Quantum Dot Cellular Automata (QCA), CMOS, FinFETs, Nanoscale

### 1. Introduction

Because of its high lithography, short channel effect, and high power consumption, the complementary metal oxide semiconductor (CMOS) technique cannot continue to increase the number of devices per chip. Due to all these drawbacks, researchers are considering alternative technologies such as quantum dots, cellular automata, and field effect transistors (FinFETs) that can operate at the nanoscale.

A new instrument in the field of nanoelectronics that has been technologically developed to allow the modeling of multidimensional quantum circuits and devices is the quantum-dot cellular automata (QCA). In QCA, unlike a conventional computer, digital information is represented as an arrangement of paired electrons that are connected to form an array of quantum dots. Boolean logic is implemented using quantum dots in the QCA designer. With advances in QCA technology, digital circuits designed using QCA have become smaller and faster, with significant power savings. Due to interactions between nearby cells, electrostatic or magnetic fields caused state changes in the QCA. QCA uses electron localization to represent binary values in quantum dots instead of a sequence of voltages and currents, as is done in traditional computers to create and model huge electronic circuits.

### 2. QCA PRELIMINARIES

#### QCA cell

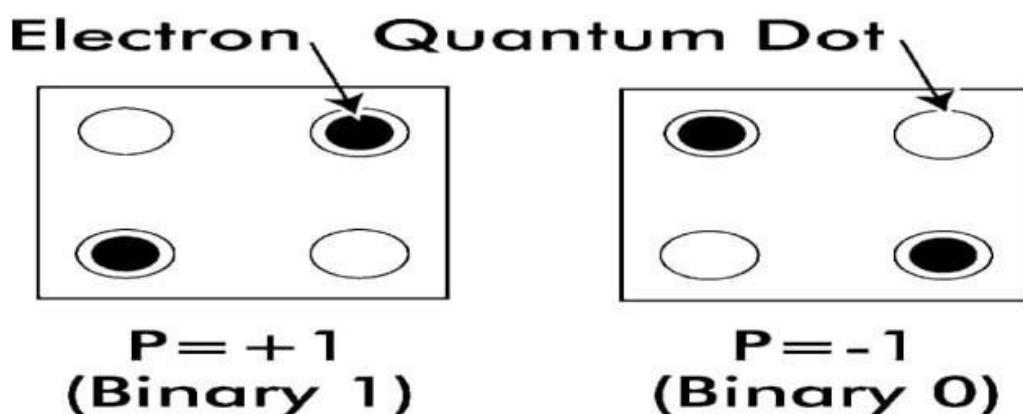

In QCA, a cell is the fundamental building block. In a QCA cell, the logical bit representation is carried out using the proper charge configuration. Each cell of a quantum dot consists of four charge carriers located at the corners of the cube. As seen in Figure 1, these four quantum dots form a QCA cell in which one of its electron pairs is located diagonally opposite another pair. Since the electrical repulsion between the electrons in QCA is weaker than in other substances, the electron pairs in QCA tend to occupy opposite corners, or diagonal locations, rather than adjacent locations.

Figure 1: QCA Cell

### QCA clock

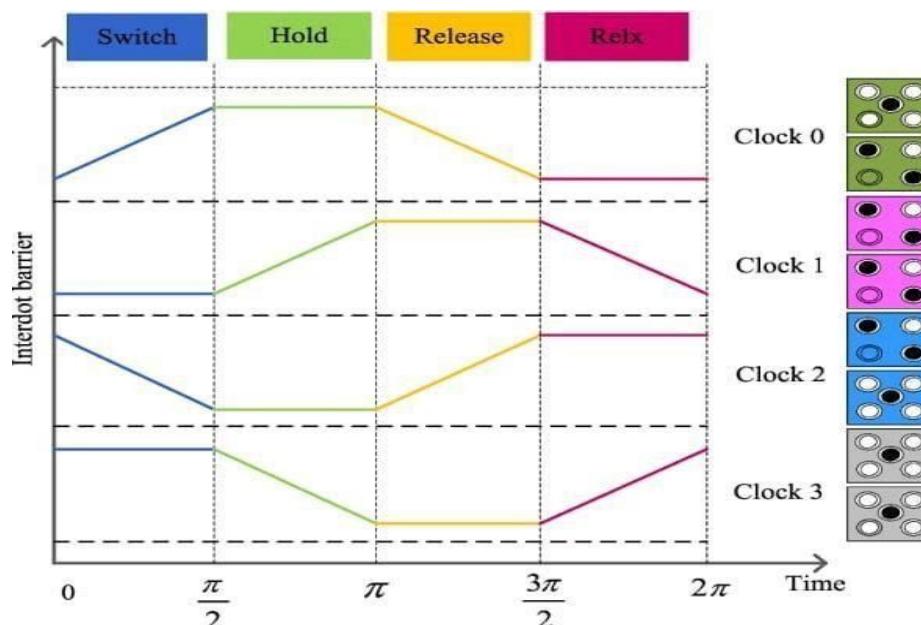

Clock-based QCA is used to perform calculations and ensure data flow to the output. Clocking is important for powering the QCA circuit and controlling the direction of data flow. The barrier between points is managed by the clock. The cell polarity is still unclear if the clock is running slowly. When the clock is high, the cell's polarity is fixed. Four clock phases are present in the clock signal to guarantee adiabatic cell switching. These phases are switching, holding, releasing, and relaxing. There are four clock zones with four phases each that make up the QCA circuit.

Figure 2: QCA Clock

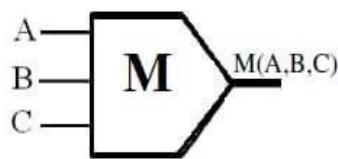

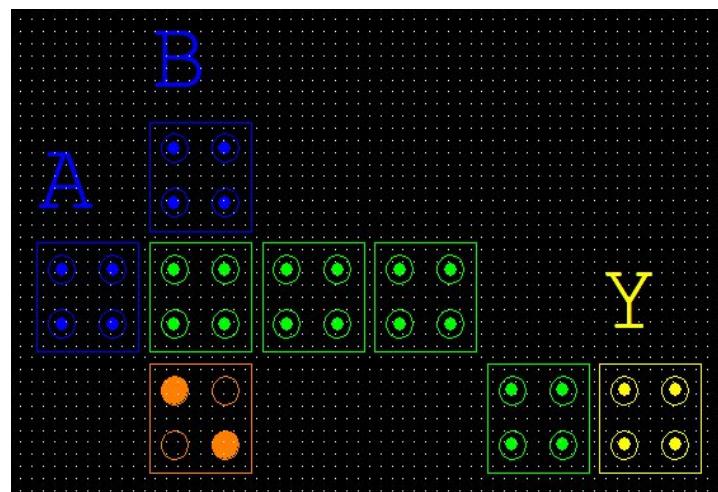

### Majority gate

The majority gate is known as the universal gate of the QCA logic. The output of a three-input majority gate is true if either of the two inputs is true, and the three inputs all have the same priority. Five QCA cells are arranged in a cross pattern to create the majority gate, as shown in Figure 3. The majority gate will generate the output based on the majority of the inputs.

| A | B | C | MV |

|---|---|---|----|

| 0 | 0 | 0 | 0  |

| 0 | 0 | 1 | 0  |

| 0 | 1 | 1 | 1  |

| 0 | 1 | 0 | 0  |

| 1 | 0 | 1 | 1  |

| 1 | 0 | 0 | 0  |

| 1 | 1 | 1 | 1  |

| 1 | 0 | 0 | 0  |

3(a)

Figure 3: 3(a)Block diagram of majority gate

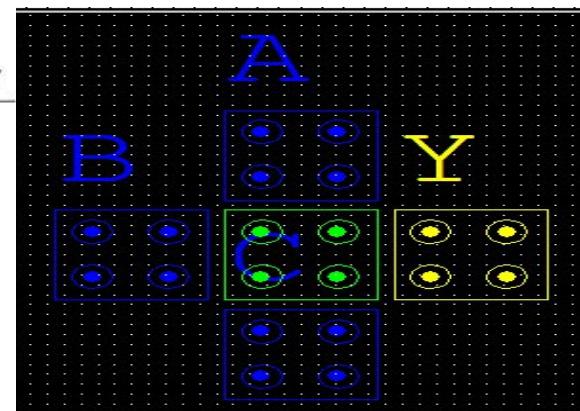

3(b)

3(b)Majority gate in QCA

### 3. LOGIC GATE DESIGN IN QCA

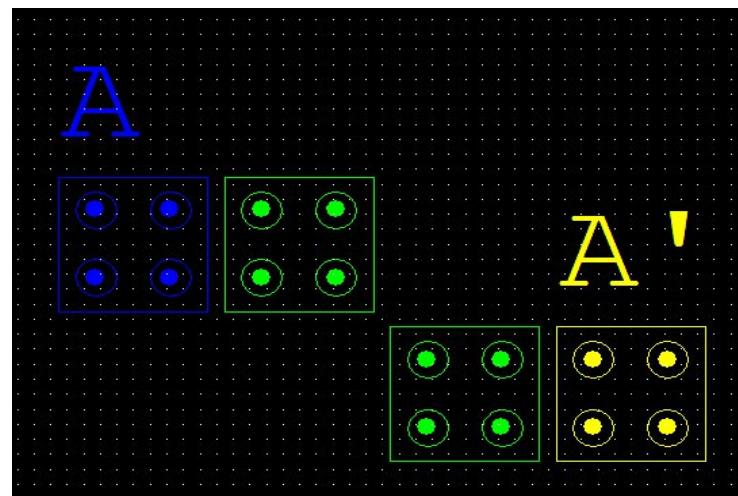

#### NOT Gate

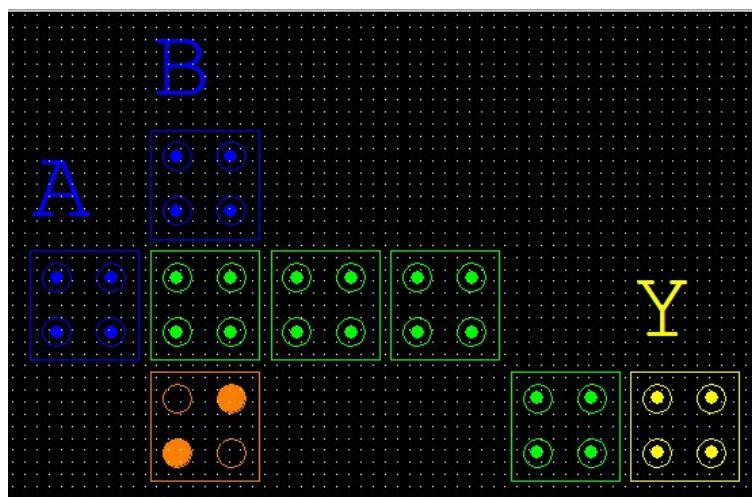

A NOT gate is a basic digital logic gate that has a single input and simple behavior. A NOT gate takes its input and negates it. That is, if the input is true, the output will be false. QCA can be used to build inverters or NOT gates by positioning two QCA cells at a 45-degree angle to one another and allowing them to interact with each other. Using the QCAD NOT tool, the gate design is represented in Figure 4.

Figure 4: NOT gate implementation using QCA

#### AND Gate

An AND gate is a circuit that allows two signals to be combined so that the output is always on if both signals are present. The majority gate in Figure 5 can be converted into an AND gate by polarizing one of the inputs to zero. The solution is  $M(A, B, 0) = AB$ .

**Figure 5:** AND gate implementation using QCA

## OR Gate

Only when one or more of its inputs are HIGH does the Logic OR Gate's output go HIGH to a logic level 1, making it a particular form of digital logic circuit. The majority gate in Figure 6 can be converted into an OR gate by polarising one of the inputs to one. The solution is  $M(A,B, 1) = A+B$ .

**Figure 6:** OR gate implementation using QCA

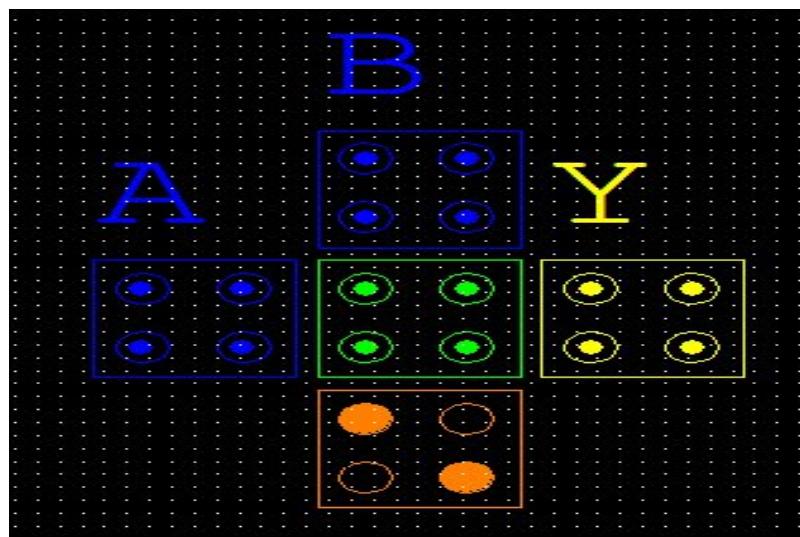

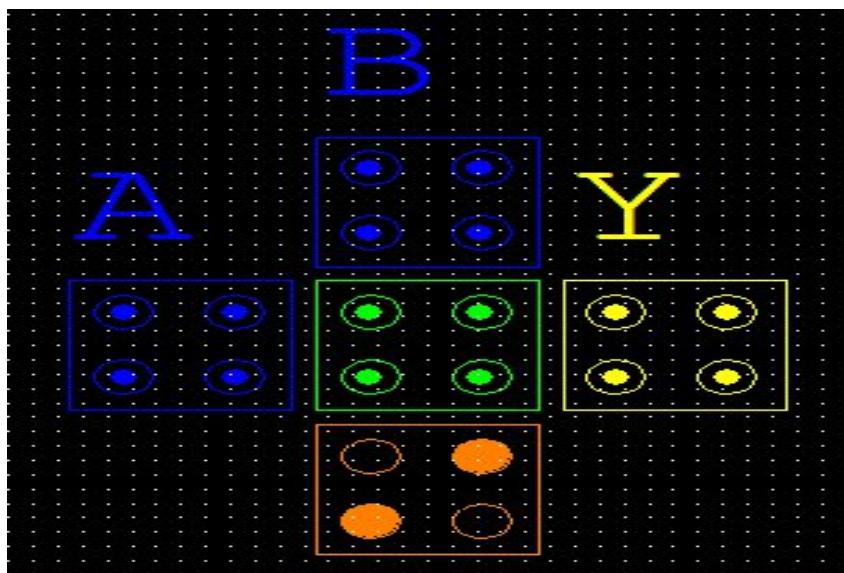

## NAND Gate

A digital logic AND gate and a NOT gate coupled in sequence make up a logic NAND gate. Figure 7 illustrates how to create a NAND gate by adding an inverter to the output of an AND gate.

Figure 7: NAND gate implementation using QCA

## NOR Gate

A digital logic OR gate and a NOT gate coupled in sequence make up a logic NOR gate. Figure 8 illustrates how to create a NOR gate by adding an inverter to the output of an OR gate.

Figure 8: NOR gate implementation using QCA

## 4. SIMULATION

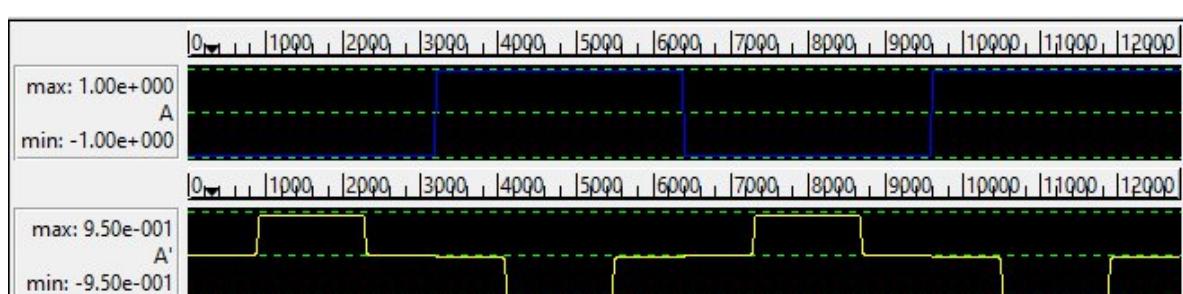

### NOT Gate

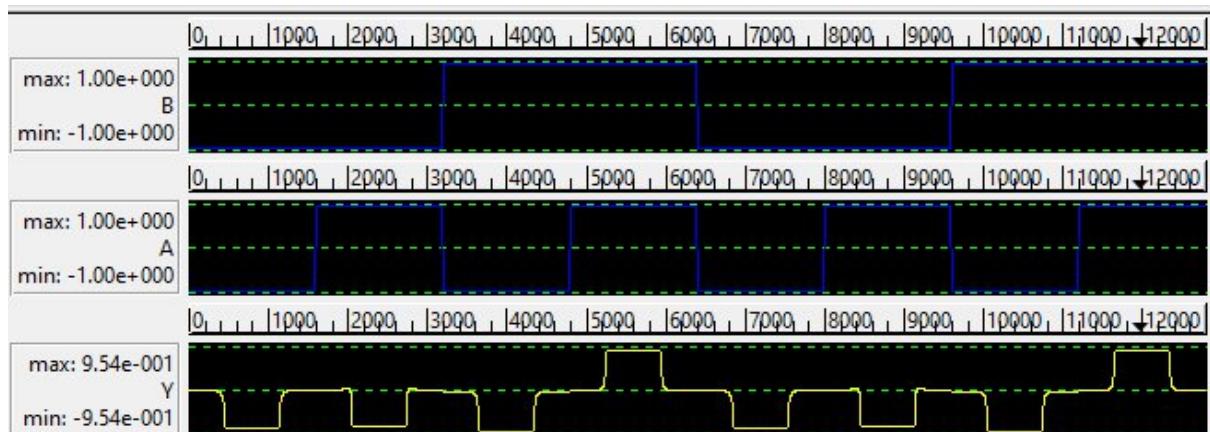

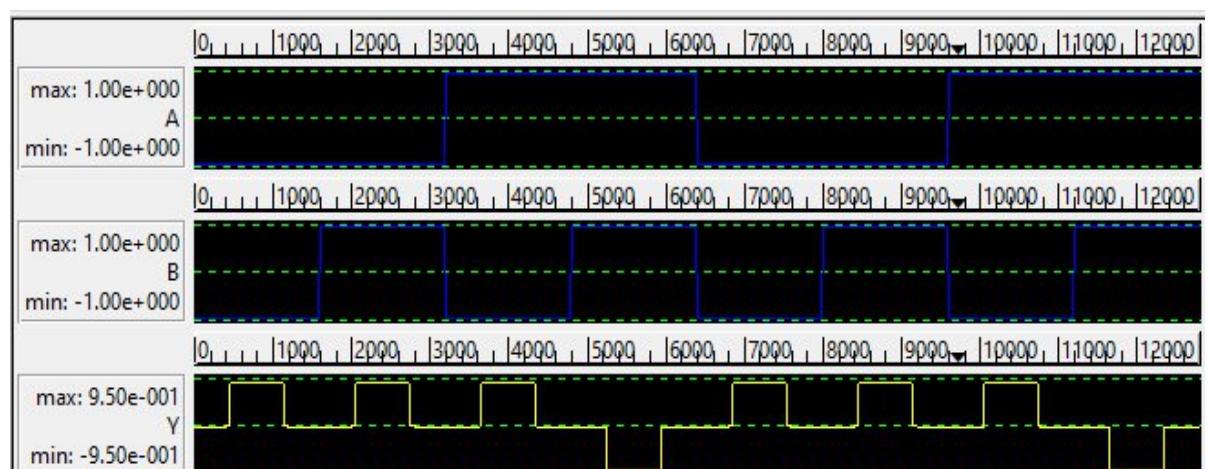

## AND Gate

## OR Gate

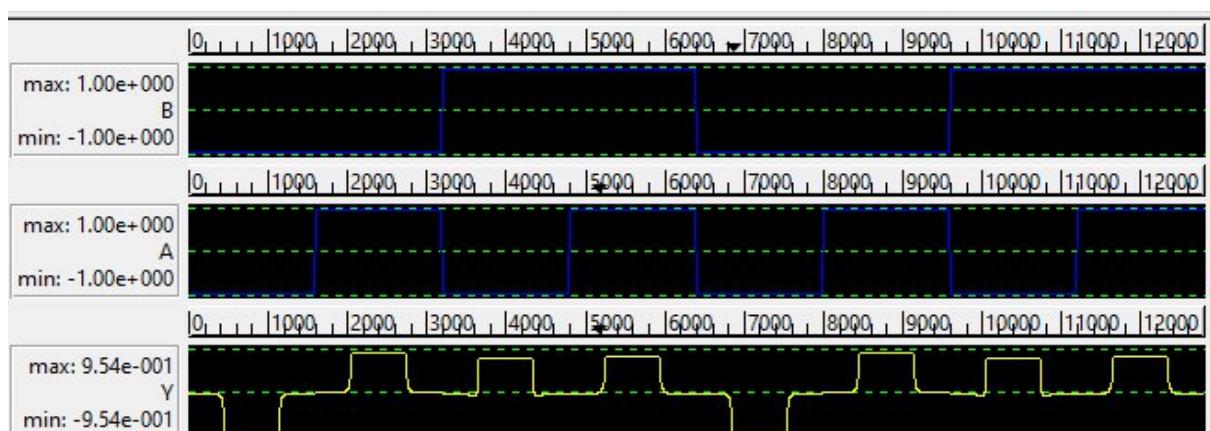

## NAND Gate

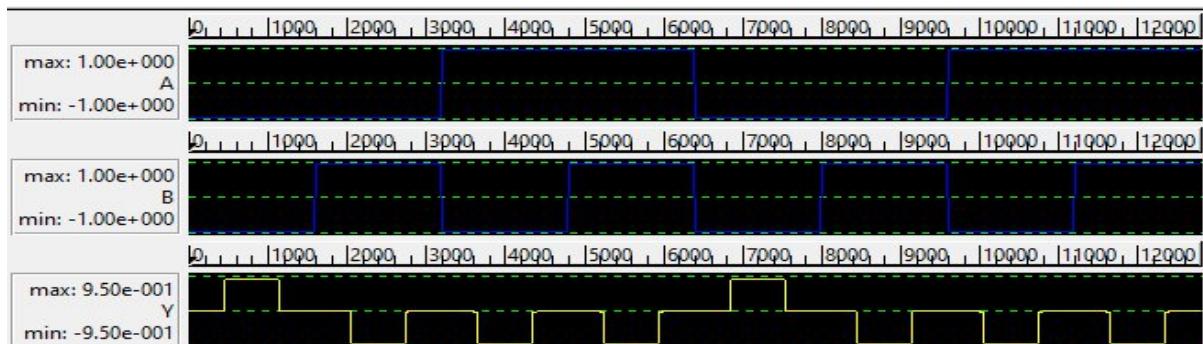

### NOR Gate

## 5. Conclusions

A novel technique for designing nanoscale circuits called quantum dot cellular automata (QCA) is appropriate for creating extremely scalable logic circuits. Since logic gates are a fundamental component of most digital circuits, it is crucial that their designs be fast, simple, and small. The proposed QCA-based digital circuits can be fabricated using fewer QCA cells and a more flexible size specification. This document illustrates how QCA design has enhanced the design and implementation of several logic gates. This is a significant improvement over all previous designs. The main goal of this study is to construct simple QCA-based logic gates with considerable adaptability and compatibility using majority gates.

## Reference

- [1] S. Bhanja, M. Ottavi, F. Lombardi, and S. Pontarelli, "QCA Circuits for Robust Coplanar Crossing," *Journal of Electronic Testing*, vol. 23, pp. 193-210, 2007/06/01 2007.

- [2] P. D. Tougaw and C. S. Lent, "Dynamic behavior of quantum cellular automata," *J of applied physics*, vol. 80, pp. 4722-4736, 1996.

- [3] M. T. Niemier and P. M. Kogge, "Designing Digital Systems in Quantum Cellular Automata," *Notre Dame*, 2004.

- [4] K. Walus, T. J. Dysart, G. A. Jullien, and R. A. Budiman, "QCADesigner: a rapid design and Simulation tool for quantum-dot cellular automata," *IEEE Transactions on Nanotechnology*, vol. 3, pp. 26-31, 2004.

- [5] J. Huang, M. Momenzadeh, L. Schiano, and F. Lombardi, "Simulation-based design of modular QCA Circuits," in *5th IEEE Conference on Nanotechnology*, 2005., 2005, pp. 533-536 vol. 2.

- [6] T. Cole and J. C. Lush, "Quantum-dot cellular automata," *Prog. Quantum Electron*, vol. 25, pp. 165-189, 2001.

- [7] D. P. Kelly and J. C. Lush, "Logic devices for partitioned quantum-dot cells," in *Proceedings of the 2001 1st IEEE Conference on Nanotechnology. IEEE-NANO 2001 (Cat. No.01EX516)*, 2001, pp. 374-379.

- [8] S. R. Kassa, R. K. Nagaria, and R. Karthik, "Energy efficient neoteric design of a 3-input Majority Gate with its implementation and physical proof in Quantum dot Cellular Automata," *Nano Communication Networks*, vol. 15, pp. 28-40, 2018.

- [9] M. B. Tahoori, H. Jing, M. Momenzadeh, and F. Lombardi, "Testing of quantum cellular automata," *IEEE Transactions on Nanotechnology*, vol. 3, pp. 432-442, 2004.

- [10] H. Hosseinzadeh and S. R. Heikalabad, "A novel fault tolerant majority gate in quantum-dot cellular automata to create a revolution in design of fault tolerant nanostructures, with physical verification," *Microelectronic Engineering*, vol. 192, pp. 52-60, 2018.

- [11] E. Alkaldy and K. Navi, "Reliability Study of Single Stage Multi-Input Majority Function for QCA," *International Journal of Computer Applications*, vol. 83, 2, 2013. \\

- [12] T. J. Fountain, "The design of highly-parallel image processing systems using nanoelectronic devices," in *Computer Architecture for Machine Perception*, 1997. CAMP 97. Proceedings. 1997 Fourth IEEE International Workshop on, 1997, pp. 210-219.